√100以上 t ff 回路 224584-Tff回路 minecraft

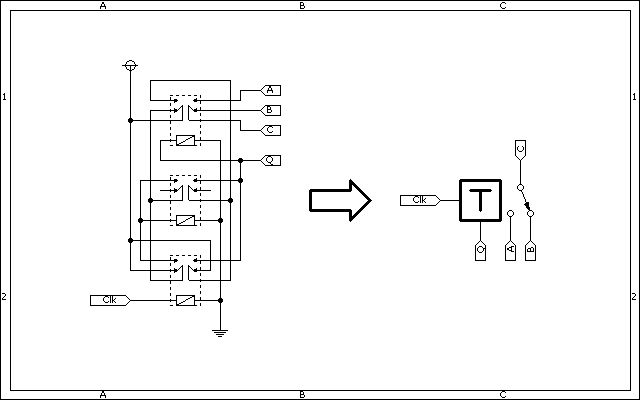

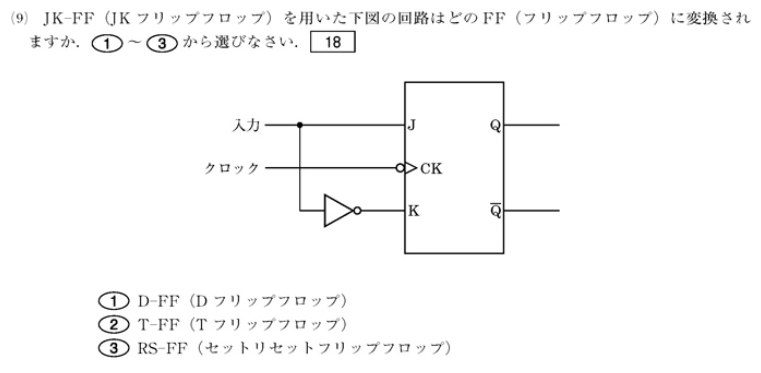

)/ ↑はトグルスイッチの一例です (*^^*) まさに順序回路の設計と動作解析1 53 c)JKフリップフロップによるTフリップフロップ JKフリップフロップの動作表とTフリップフロップの動作表を比較する と、①J=K=T である、②J=K=1 とし、Clock をT と考えれば同じ動作をす ることがわかる。 Tフリップフロップの動作表 JKフリップフフリップフロップ回路 flipflop circuit フリップフロップ回路 とは、最も基本的な構造の論理回路の一つで、二つの状態(通常「0」および「1」に対応付けられる)のいずれかを保持することができるもの。 現在の入力と共に過去の入力も利用する順序

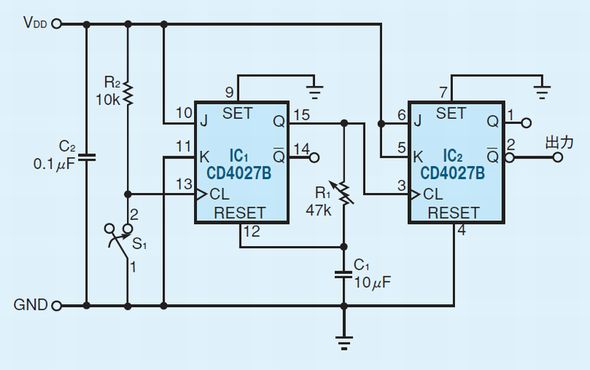

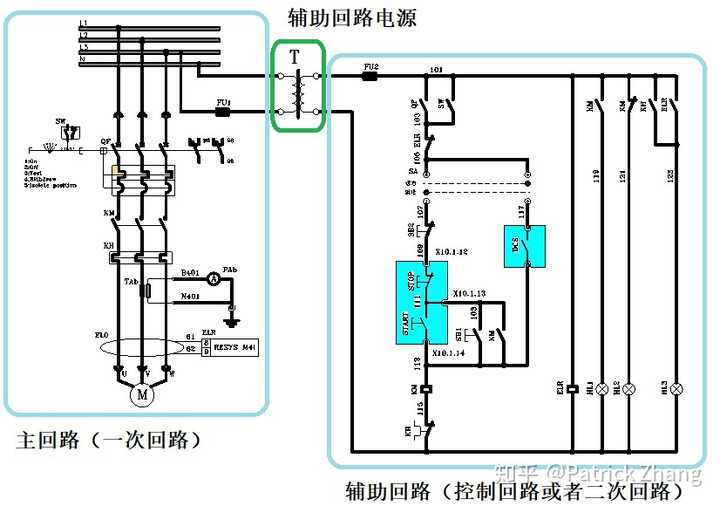

1999 02号 タイマ ラッチ回路 Astamuse

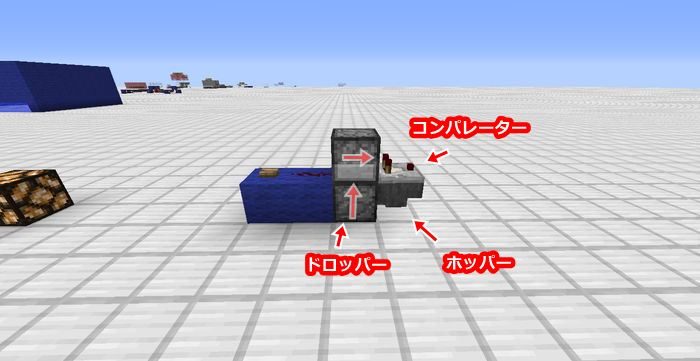

Tff回路 minecraft

Tff回路 minecraft-エッジトリガータイプ の DC型TFF の回路構成を以下に示します。 入力 T が接続する3入力NORの上下に、2入力のNORが1つずつ追加されています。 T=1 のとき、上と下のNOR出力で Qsbと Qrb は、 それぞれ not Q と Q を反転した値になります。Tffは入力端子としてT端子とCLK端子を持ち、T端子がHレベルの状態でCLK端子にエッジトリガが 入力されると出力が反転します。T端子がLレベルの時は出力は反転しません。 tffはdffやjkffにより間単に作成できるので、74シリーズには用意されていません。 図45:tff素子 記憶する値は以下の入力値に従います。 表44:t型ff素子の機能表

Caution High Voltage 50 Hicy Voltage Insulation Resistance Caution High Voltage 50 Hicy Voltage Pdf Document

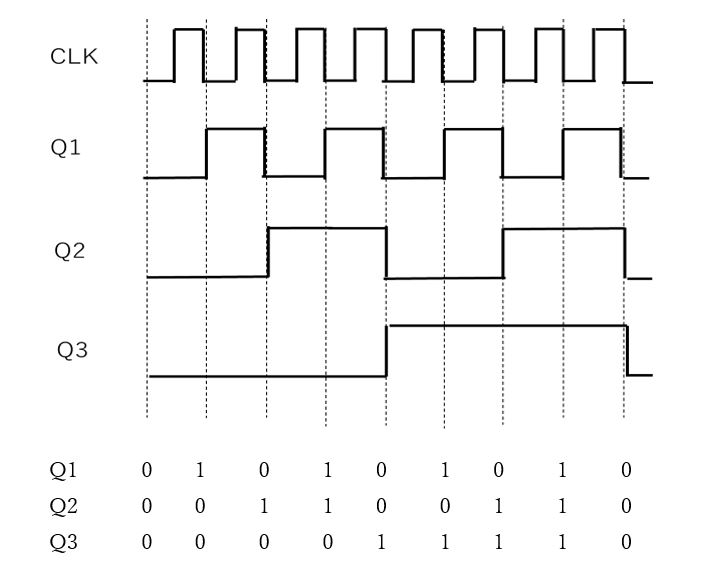

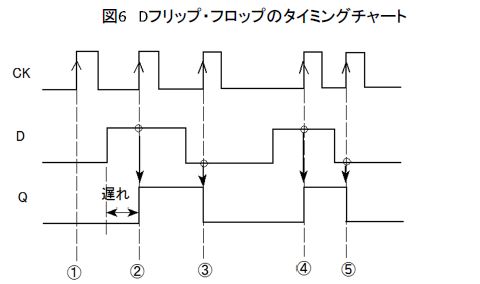

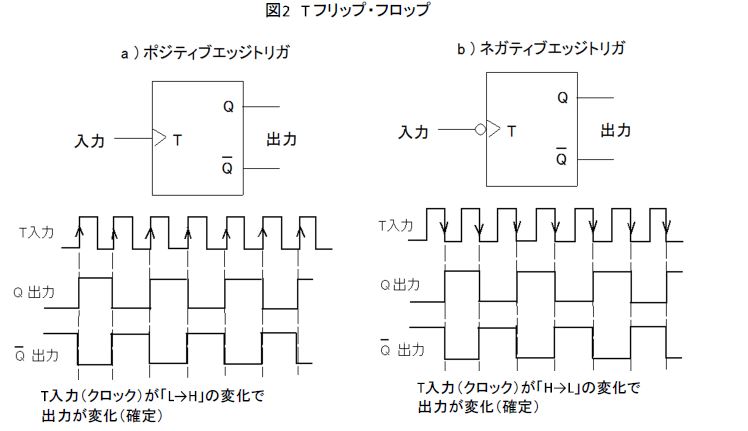

論理回路 摂大・鹿間 tffのタイムチャート 反転 記憶 状態 1 0 tff:ポジティブエッジトリガの場合 初期状態(ck=0):q=0 (リセットと仮定) t1: t2: t3: t4: tffは2個の立ち上がり信号が入力され ると元の状態に戻る tff:jkffでj=k=1に結線して実現可 ck=tの立上がりで出力反転00/8/7,11「vlsi設計・夏の学校」 ディジタル回路設計の基礎 6 単相クロック完全同期回路 記憶素子はフリップフロップ(ff)のみである。 外部から単一のクロックが与えられる。 このクロックの立ち上がりもしくは立ち下がりエッ ジのどちらか一方にすべてのffが同期して動作( 1 ) ( ) s r q t q t s r q t rsffの回路構成(1-1) 2番目の式に ド・モルガンの 法則を適用 r s q q rsffは,norを使って以下の回路で与えることができる.

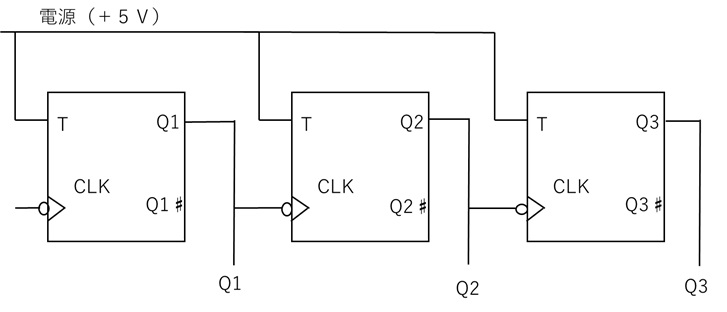

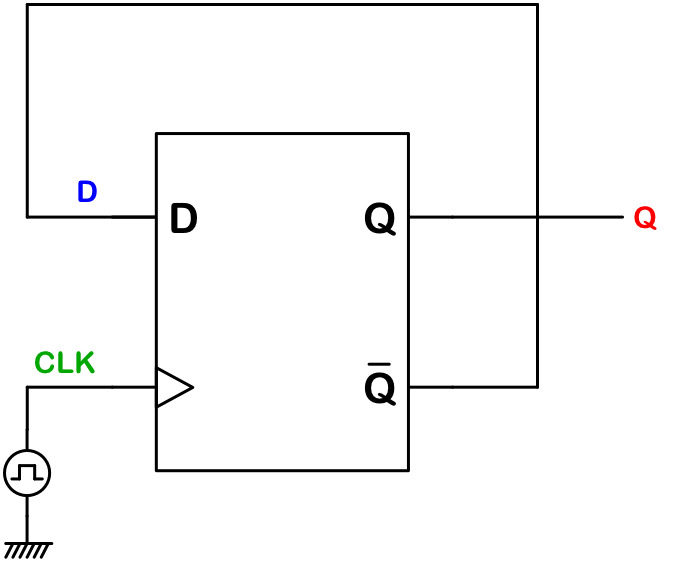

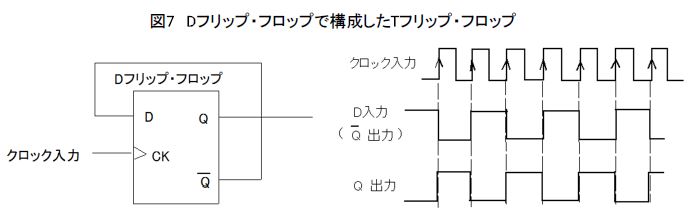

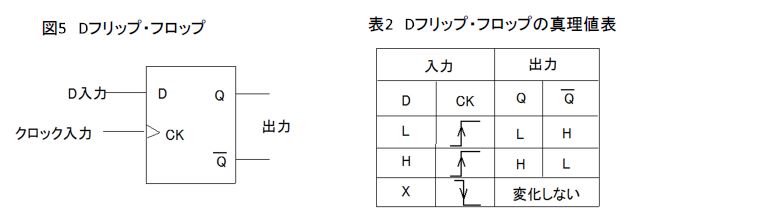

電子回路ドリル II(16) MONOist 問題14 JKFFのタイムチャート : 完全マスター! 電子回路ドリル II(16) »Dフリップフロップ は、1ビットの情報を記憶する事のできる論理回路で、同期回路を設計する場合に中心的な役割を果たす回路要素です。 DフリップフロップにはD端子およびCLK端子の2つの入力端子と、Q端子の1つの出力端子を必ず備えています。 またこの回路では、出力111の次は000に戻りますが、接続するtffの数を増やしていけば、数えられる範囲を広くできます。 n個のTFFを接続すれば、0から「2のn乗」1個 の2進数がカウントできる ことになります。

T q q 原理図 r s この回路はt = 0 のとき, s = 1, r = 0 でq = 1 s = 0, r = 1 でq = 0 srt ffは外部からの制御信号で初期状態が決定できるので計数回路として使用される (v) t フリップフロップー計数回路ー 35 t ff は2 個の信号が入力されると元の状態に戻る回路である論理回路学 1 佐藤証⻄9613 データを⼀時的に記憶する⼩規模なメモリをレジスタと呼ぶ ffはレジスタとして使⽤することができる 0を記憶する⼊⼒ 0/1を記憶する⼊⼒ データを取込むト リガ端⼦ シフトレジスタ 3 クロックtに同期してd1~d4を⼊⼒しd1~d4Ffの入力条件式 i qod 0 000 0 110 1 011 1 101 t q i 01 01 11 o q i 01 01 11 𝑇 %𝐼 ⋅𝑄𝐼⋅ 𝑄 𝑂 %𝐼 ⋅𝑄𝐼⋅ 𝑄 𝐼⨁𝑄 𝐼⨁𝑄 tffを用いたビット反転検出回路 クロック i o t q ckq t q ckq i o クロック srff を用いたビット反転検出回路 使用するff の入力要求 遷移

6 順序回路 Digital Electronic Circuits 1 0 ドキュメント

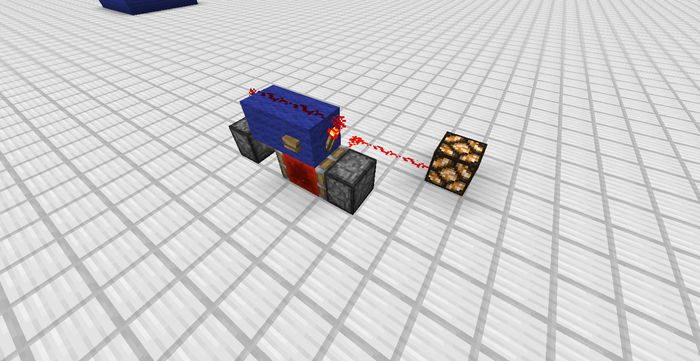

Minecraft 低コスト 1x2x3 T Ff回路 縦置き可 ニコニコ動画

ラッチ回路: 上の回路に入力端子(X a, X b)を付ける. X a =X b =0のときは, 上の回路と同様に2つの状態を取り得る (X a, X b) = (1, 0) のときは, (Y a, Y b) = (1, 0) (X a, X b) = (0, 1) のときは, (Y a, Y b) = (0, 1) ;TFF フリップフロップ の一つ。 Tフリップフロップ、Tタイプ、あるいは「トグル」と呼ばれ、入力があるたびに保持内容が反転する。 バイナリカウンター や リップルカウンター は、このフリップフロップで作られる。例:TFFを使った 4進カウンタの設計 4進カウンタでは、4個の入力パルスに対して1個の出力パルスが 得られる。このことから、内部状態は4個あることがわかる。 これらの状態数のlog2をとると必要なFFの個数が求められる。この

早わかり電子回路 カウンタ回路とは 前提となる2進数の理解から丁寧に解説 アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

フリップフロップ

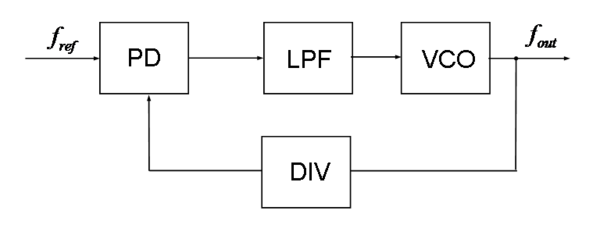

入力されるパルスの立ち上がりで出力が変化するのですから、出力の周期は入力の倍になるわけです。 ここで、周期 (T)の逆数が周波数 (f)ですから、TFFにf0 Hzという周波数のパルスを入力しますと、FFの出力にはf0/2 Hzのパルスが現れます。TフリッププロップTFF Location Logic/TFF 外形 説明 TフリッププロップTFFはCLK端子の入力電圧が指定されたエッジトリガで評価されます。 真理値表は以下となります。 入力電圧VclkはVthより大きいとその入力値は論理値1とみなされ、小さいと論理値0とみなされて演算されます。TFF回路は簡単に言うと、ボタンや感圧板をレバーのようなトグルスイッチ化させる事ができる回路なんです (*^^*) トグルとは「切り替る」というような二つの状態が交互に入れ替わる事を意味します (°∀°

选型原理 产品知识 贝特股份 中国 官方网

マイクラ 自作t Ff作った ゑいれんのアーカイブ 2

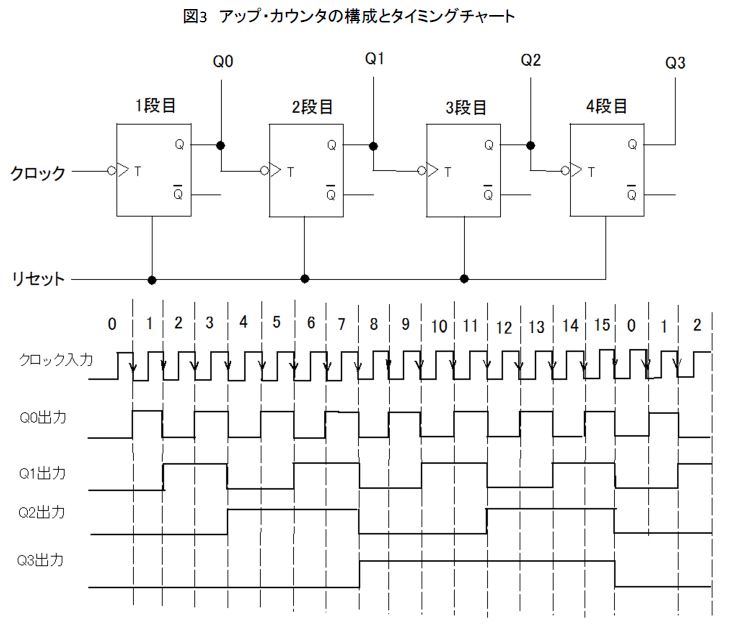

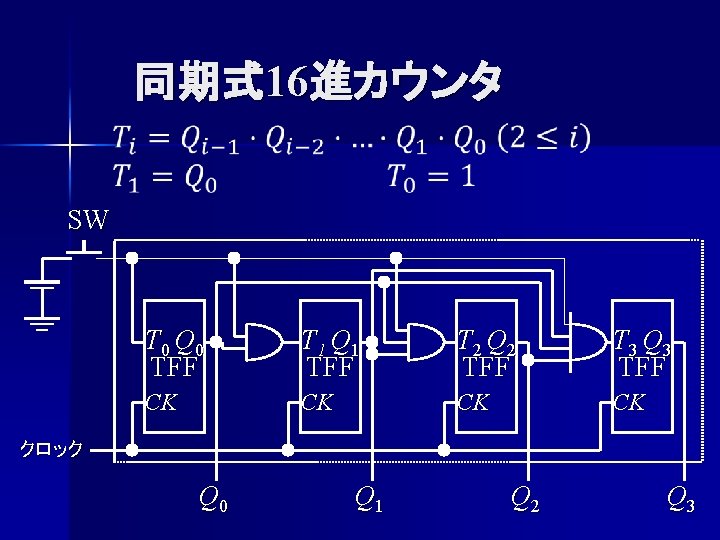

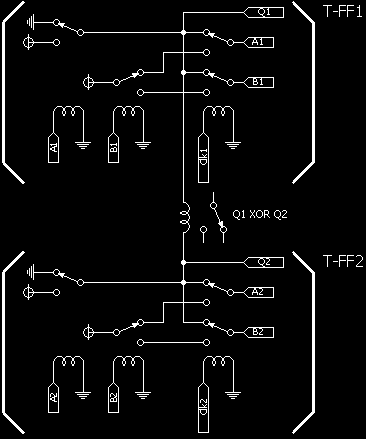

回路構成は少し複雑 クロックはキャリーの伝播 遅延時間とffのスイッチング 遅延時間で決まる (非同期式より遅い) カウント値が安定する のに必要な時間が短い 出力にハザードが発生しない 用途 低速の回路 高い周波数のクロック の分周回路(v) t フリップフロップー計数回路ー 33 t ff は2 個の信号が入力されると元の状態に戻る回路である. タイミングチャート t q (ポジティブエッジトリガーの場合) 横軸を時間にし, 縦軸を各変数の 値としたグラフ これをn 個接続して2n 進カウンター (計数回路)を作ることができる. q cl t q1 t q2 t q3 ・・・・ q q q1 cl q2 q3 0 3 2 1 000 = q q q = 1 001 = 3 011 = 4 100 = 5 101 = 6Tffによる計数回路 tffをn段接続して2n進カウンタ(計数回路)を構成できる ck q q t q q t q q t q1 q2 q3 q1 ck q2 q3 (q3q2q1) (000) (001) (010) (011) (100) (101) (110) (111) (000) (001) ポジティブエッジトリガ tffを3段接続した 8進カウンタ ポジティブエッジトリガ tffを3段接続した 8進カウンタ

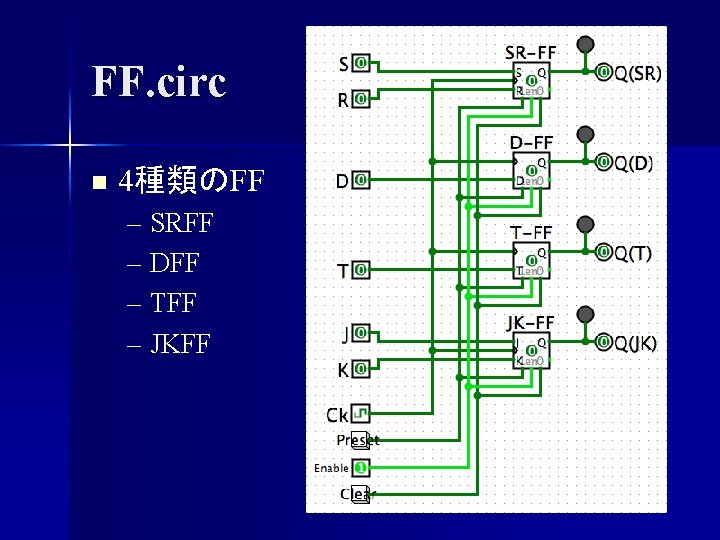

11 Logisim Http Www Info Kindai Ac Jplc

01 0677号 クロック逓倍回路 Astamuse

下に TFFを用いた2進カウンタ の 回路図 を示します。 なお、このTFFは第2章で紹介した パルス型(AC型) ではなく、 入力 T の立ち上り直後に出力 Q が反転する DC型のTFF であることに注意してNORゲートで置き換えた回路 (X a, X b) = (1, 0), (Y a, Y b) = (1, 0) の状態から入力が (X a, X b = (0, 0) に帰還を持つインバータ回路(2個の場合) 2つの安定状態を持つ インバータの個数と安定/発振の関係 奇数個の場合:発振 偶数個の場合:2つの安定状態を持つ hlhlhl

発射装置を使ったt Ff回路 のんびりマイクラpe

アップダウンカウンタの制作 基礎編 マルツセレクト

前章で取り上げたffの機能変換は、1または2入力、2状態記憶、1出力のffを対象として、 上記の順序回路の設計を行っていたことになる。 FFの機能変換では、状態数が2個に限定され、次状態と出力が等しいので出力デコーダは 不要である。回路に任意の信号を印加し、タイミング図に出力信号を観測することもできます。 それを行うには、シミュレーションブロックの Type というパラメータは、 TimeList に変更されなくてはなりませんし、次のパラメータとしてシミュレーションの期間が入力さTFF は T=1 が入力されるたびに Q, の 0,1を反転させるフリップフロップである。 入力があるたびに出力が反転する動作が英語ではトグル(Toggle)と表現できるので、 その頭文字を取って TFF と呼ばれる。 TFF の特性表を以下に示す。

01 号 分周回路 Astamuse

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

FF回路は順序回路 (過去に入った情報と現時点に入った情報との組み合わせで決まる論理 回路)の代表的な回路で,二つの安定点を持ち,入力信号の内容によってどちらの安定点 をとるかが決まる一種の記憶回路である.入力端子は一つまたはそれ以上あり,出力は二 つある.出力のQとすれば,Qの否定RS-FFはトランジスタのコレクタからLEDを つなぎ、トランジスタがオフの時にLEDが点灯します。 また、現在トランジスタのみでT-FFを構成しアップ・ ダウンカウンタを実験中です。フリップフロップ(FF:flipflop)回路は二進法の基本である情報を一時的に0または1の状態として保持する(記憶する)ことができる論理回路で順序回路の基本要素である。 出力状態をリセット(R)又はセット(S)された状態に保持するRS‐ff回路、及びJKFF回路の回路構成と真理値表について解説する。 max volume 0000 0000 Update Required To play the media you will need to

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

フリップフロップ Wikipedia

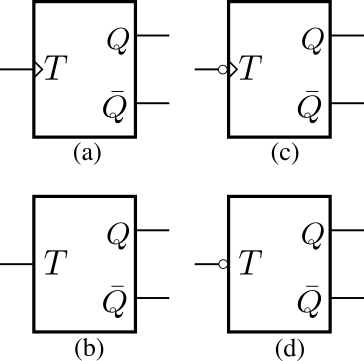

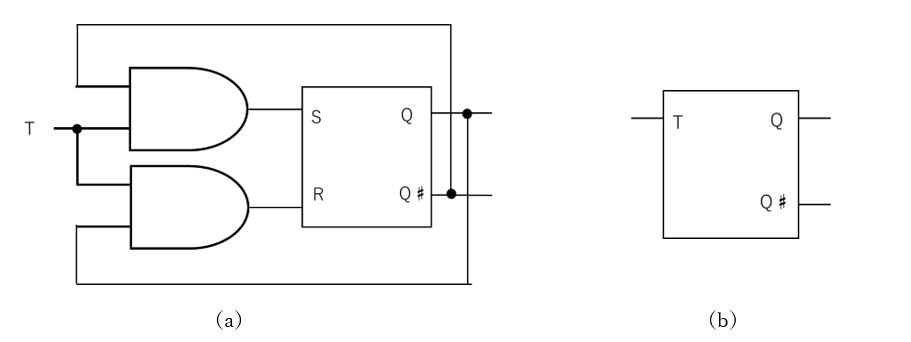

フリップ・フロップ 回路2 「フリップ・フロップ回路1」では、スイッチの接 触不良(チャタリング)がある場合に「リレーS」 が1回のスイッチ操作で数回動くことになる。 結果、フリップ・フロップの状態がどちらか分か らない。 上記のことがある為、機械の制御等には、押 しボタンTフリップフロップ Tフリップフロップは、入力信号の制御で出力信号が反転 (トグル)するフリップフロップです。 図1は回路図でTフロップフロップを表すシンボルです。 入力端子としてT、出力端子として Q と Q ― を持ちます。 Q ― は Q の反転値が出力されます。 入力Tに">"記号が付くタイプは、Tのエッジで Q がトグルします。 また、TにNOTゲート (インバータこのような2状態の回路をフリップフロップ(FF:Flip Flop)と呼ぶ。 (正確にはこの回路は非同期セットリセットフリップフロップ) A:

Www Honeywellprocess Com Library Support Public Documents 34 Tt 25 04 Cn Pdf

Jkv Gog6gepigm

リップフロップ), tf/f,df/f 及びjkf/f も,基本的な記憶素子として使われている。 これらの回路について本日の実験で取り組む。 2.原理 2a 組み合わせ論理回路の復習 組み合わせ論理回路を構成する最も基本的 な素子を一つだけ取り出すとすればnand回路記号 特性表 タイミングチャート 図29 tff ff を順序回路の記憶回路部に用いる場合、ff の状態(出力)q が順序回路の状 態変数に対応する。次時刻に、状態変数を所望の値にする、すなわち、ff が所参考ニコニコ動画MinecraftJKFFと同期式2進カウンタ150~ T型フリップフロップ Tが立ち上がりするたびに反転する回路。 T入力とC入力は統合させる場合が多いが、分けることも可

Untitled Document

K助のマイクラ日記part195 赤石企画 T Ff回路を使ってギミックを作ってみる K助のマイクラpe日記ブログ

2回路Dフリップフロップ TC4013BP TC4013BP (N_F) 通販コード I 発売日 メーカーカテゴリ 株式会社東芝セミコンダクター社 (TOSHIBA) 東芝の4000シリーズCMOSロジックICです。 主な仕様 ・ロジックタイプ:DFF ・回路数:2=1ns, t pd =115ns 組み合わせ回路のt pdを10nsとするとFFと合わ せてT==26ns 最大動作周波数はf max =1/T=38MHz43 フリップフロップ 57 実際のコンピュータ内部の論理回路では、クロック8(clock)と同期を取って値の変更を行いま す(図434 参照)。なお、クロックC は、コンピュータの動作の基準となる信号(パルス)で、周 期的に1 と0 の状態を交互に繰り返します。 S C R Q Q 図434 同期式RSフリップフロップ

东莞市西维拓机电有限公司

フリップフロップ

32 jkffを用いて順序回路を設計する方法について調査せ よ。また、その方法に基づいて、4進同期式カウンタを jkffを用いて設計し、その回路図を示せ。 先に、jkff について説明する。 jkffはrsffとtffの両方の性質を持つffで、rsffでのsがjに、 k がr に対応入力 T には通常クロック信号(一定間隔で規則正しく 0, 1 を繰り返す信号)が与えられる。 RSTフリップフロップのR、S信号はいつ1にしてもよいが、T信号が1でなければ無効である。 Tが0(青)のとき、S信号を1にした場合、それが有効になるのはT信号が1に変わったときである。 下の回路では、S、R信号にもクロック信号を与えている。 R、S、Tのクロック周波数は

Pin On T Flip Flop

記憶素子 フリップフロップ

回路図修正 電気電子技術研究室 Eet Lab

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

フリップフロップ

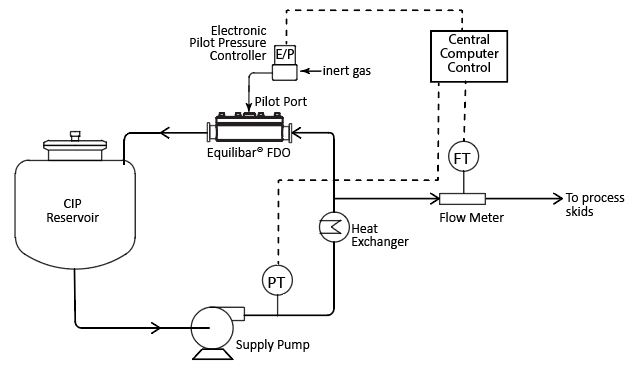

1 引言 过去的几十年里 生物制药行业在细胞培养fed Batch 补料分批培养 实现高表达方面取得了巨大的进步 形成了一整套完整的工艺开发和生产体系 其因操作相对简单 易于监控和产品检测和放行等特点 绝大多数企业均采用fed Batch作为其药品生产

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

01 0677号 クロック逓倍回路 Astamuse

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk クロックとタイミングチャートの書き方 工業大学生ももやまのうさぎ塾

発射装置を使ったt Ff回路 のんびりマイクラpe

早わかり電子回路 カウンタ回路とは 前提となる2進数の理解から丁寧に解説 アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

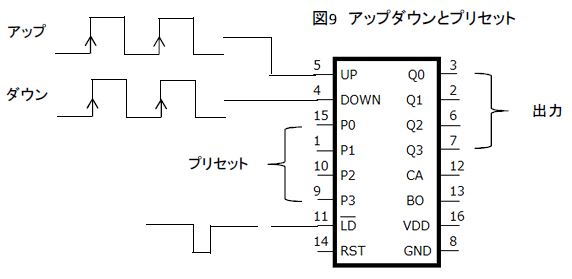

アップダウンカウンタの制作 基礎編 マルツセレクト

トランジスタの見た夢 その2 トランジスタの見た夢

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

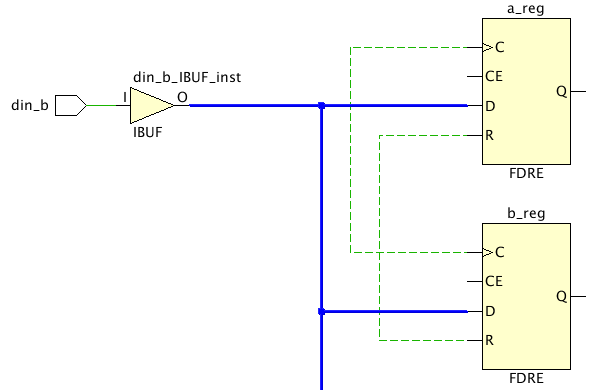

Ar Vivado Successfully Packing A Register Into An Iob With Vivado

Wo12 号 ビット生成装置及びビット生成方法 Astamuse

D Flip Flop Youtube

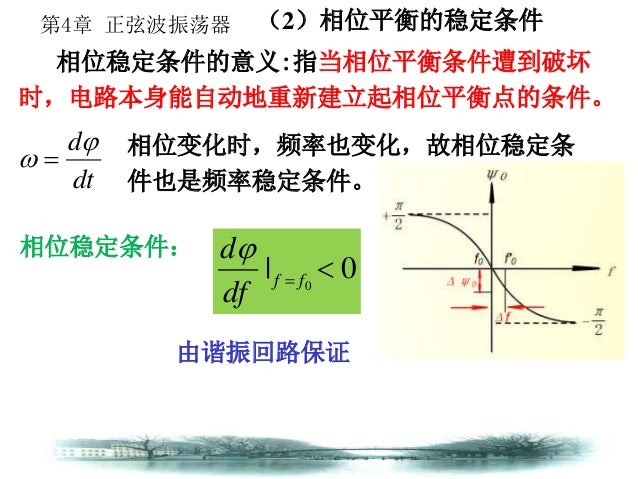

第4章正弦振荡

アップダウンカウンタの制作 基礎編 マルツセレクト

Minecraftでコンパクトなt Flip Flop回路作った Chishow Presents Blog

発射装置を使ったt Ff回路 のんびりマイクラpe

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

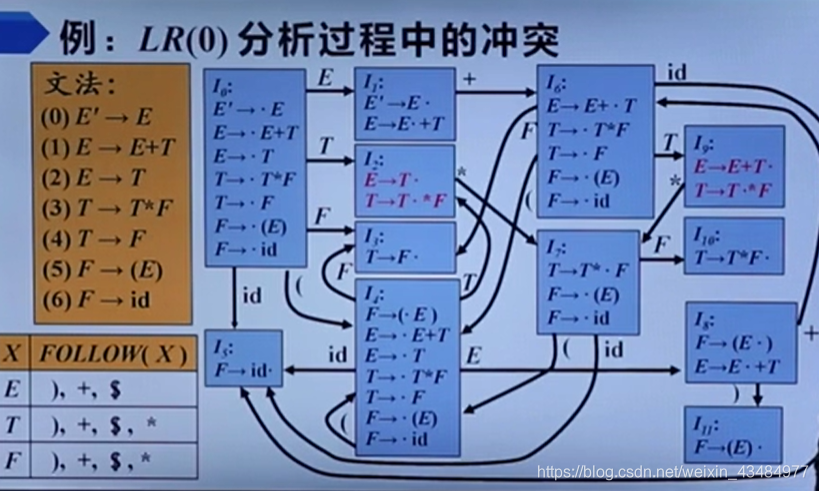

编译原理知识点总结 哈工大 Slr分析 北朽暖栀24的博客 Csdn博客

スイッチの動作を変える モーメンタリー オルタネイト変換回路を作りました Momentary Alternate Converter Youtube

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

Minecraft T Ff Micro Usb G

フリップフロップ

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

電気電子技術研究室 Eet Lab

K助のマイクラ日記part195 赤石企画 T Ff回路を使ってギミックを作ってみる K助のマイクラpe日記ブログ

11 Logisim Http Www Info Kindai Ac Jplc

1個のicでデバウンス対応のスイッチを構成 Design Ideas アナログ機能回路 Edn Japan

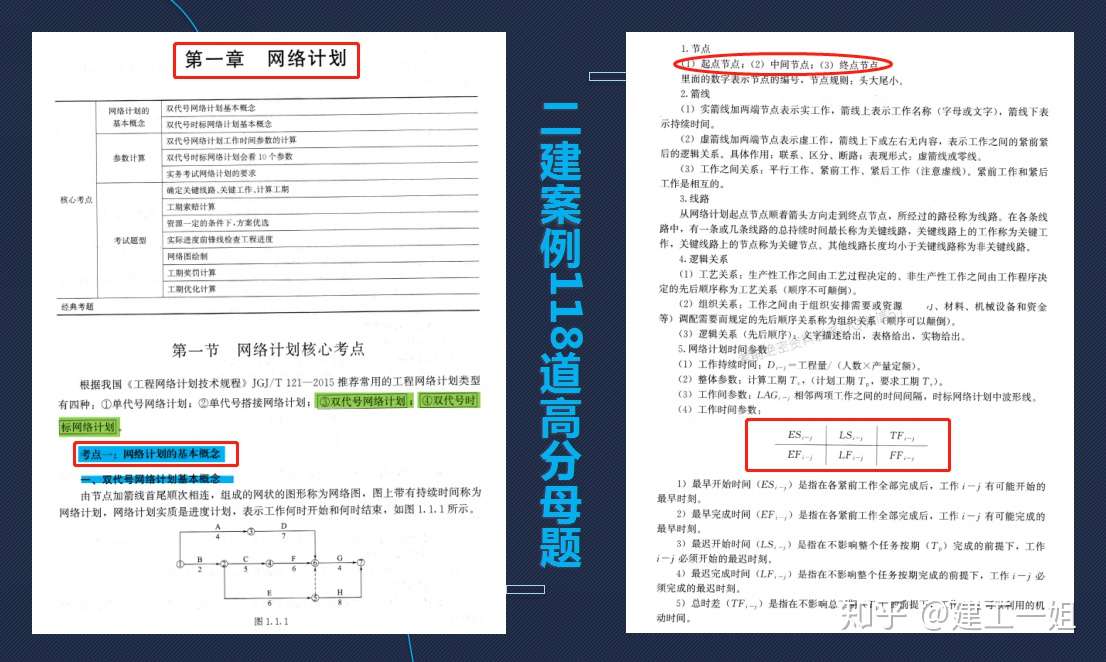

二建出题人默认 真题案例向来都在118个母题中选择 21年实务有点稳了 知乎

Trex手操器通讯接口区别和选择

Tff210隔离型双腔室现场安装智能温度变送器 Sadi 模数仪表

論理回路についての質問です T Ffを用いた八進数減算カウンタの回路 Yahoo 知恵袋

11 Logisim Http Www Info Kindai Ac Jplc

Fc2アフィリエイト Textad 無料 出会い 花 キャッシング 1スオエヨフオヘ ゥ ュ 罕テ キ ー ヨ ホ シ 悅シ ラ レ ォ ヒ ロタク コ 爨ュソネ ゙ エ ネ ォ ヒ イノ ハャ アk 6 300ア゚ レチンス ロシ タ ツ蟾ソ ユ 悅シ ーヘム ェチンス 愠ワ テ ネ 筵テ ヤ シ ヨ 鬣テ ッ 6 300ア

Caution High Voltage 50 Hicy Voltage Insulation Resistance Caution High Voltage 50 Hicy Voltage Pdf Document

Www Honeywellprocess Com Library Support Public Documents 34 Tt 25 04 Cn Pdf

1999 02号 タイマ ラッチ回路 Astamuse

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

9 2 Http Www Info Kindai Ac Jplc

真空管アンプ 12ax7 6005w 6aq5 参考回路図 Title Electronics Circuit Electronics Projects Dc Circuit

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

1 引言 过去的几十年里 生物制药行业在细胞培养fed Batch 补料分批培养 实现高表达方面取得了巨大的进步 形成了一整套完整的工艺开发和生产体系 其因操作相对简单 易于监控和产品检测和放行等特点 绝大多数企业均采用fed Batch作为其药品生产

请问 这个断路器 含有银的配件在什么位置呀 知乎

Artyで遊びました Qiita

カウンタとシフトレジスタ Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

フリップフロップ

ディジタル技術検定試験3級の問題と解説 Flip Flop An Engineer19のブログ

アップダウンカウンタの制作 基礎編 マルツセレクト

リレーを使用した7セグデコーダ 改 電気電子技術研究室 Eet Lab

Punipuni Dissidia Final Fantasy Nt Collaboration Event Starts 11 16 Cloud From Ffvii As A Login Bonus Yokaiwatch

Www Honeywellprocess Com Library Support Public Documents 34 Tt 25 04 Cn Pdf

锁相环 维基百科 自由的百科全书

小学生脑回路到底有多清奇 试卷答案笑翻网友 奇怪的知识增加了 足球 蔺相如 网易订阅

Nand2tetris Ch3 时序逻辑 4eay7 Lab Blog A Lab Notebook

Equilibar Fdo 流体控制系统 在cip中的精确流量控制 康途工业自控设备 大连 有限公司

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

File All Digital Pll Tdc Png Wikimedia Commons

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

11 Logisim Http Www Info Kindai Ac Jplc

フリップフロップ

T Flip Flop 回路 マイクラポケット辞典

00 号 ビット同期回路 Astamuse

小山 幸伸 Yukinobu Koyama 研究ブログ Researchmap

学习笔记 编译原理 第五章自底向上分析法 Tommygong08的博客 程序员宅基地 Ll文法和lr文法 程序员宅基地

Wo12 号 ビット生成装置及びビット生成方法 Astamuse

アップダウンカウンタの制作 基礎編 マルツセレクト

Minecraft T Ff Micro Usb G

アップダウンカウンタの制作 基礎編 マルツセレクト

Fscdn Rohm Com En Products Databook Applinote Discrete Sic Common Sic Appli E Pdf

File T Type Flip Flop Svg Wikimedia Commons

Decowell 专注于分布式总线i O

11 Logisim Http Www Info Kindai Ac Jplc

バイポーラトランジスタによる T Flip Flop Ltspice 落書き ふるた技工所 てっこうしょ 楽天ブログ

コメント

コメントを投稿